- 您现在的位置:买卖IC网 > Sheet目录3873 > PIC16F884-I/ML (Microchip Technology)IC PIC MCU FLASH 4KX14 44QFN

2009 Microchip Technology Inc.

DS80302F-page 11

PIC16F88X

9.

Module: LP/Timer1 Oscillator Operation

Below 25°C

1-2% of devices experience reduced drive as

temperatures approach -40°C. This will result in a

loss

of

Timer1

counts

or

stopped

Timer1

oscillation.

This can also prevent Timer1 oscillator start-up

under cold conditions.

Work around

Use of low-power crystals properly matched to the

device will reduce the likelyhood of failure. A 1m

Ω

resister between OSC2 and VDD will further

improve the drive strength of the circuit.

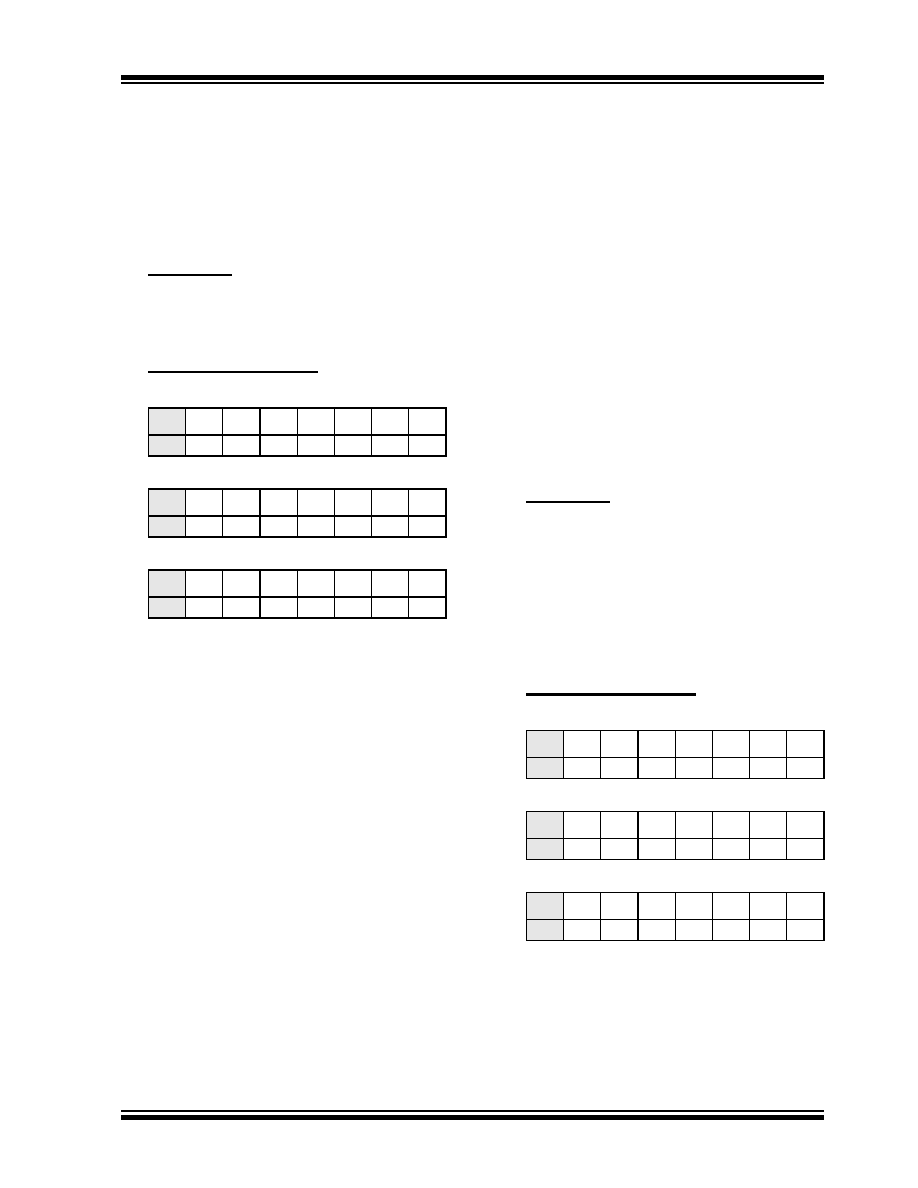

Affected Silicon Revisions

PIC16F882

PIC16F883/PIC16F884

PIC16F886/PIC16F887

10. Module: Timer0 and WDT Prescaler

Assignment Spurious Reset

A spurious Reset may occur if the Timer0/

Watchdog Timer (WDT) prescaler is assigned

from the WDT to Timer0 and then back to the

WDT.

Summary

The issue only arises when all of the below

conditions are met:

Timer0 external clock input (TOCKI) is enabled.

The Prescaler is assigned to the WDT, then to

the Timer0 and back to the WDT.

During the assignments, the T0CKI pin is high

when bit TOSE is set, or low when TOSE is

clear.

The 1:1 Prescaler option is chosen.

Description

On a POR, the Timer0/WDT prescaler is assigned

to the WDT.

If the prescaler is reassigned to Timer0 and

Timer0 external clock input (TOCKI) is enabled

then the prescaler would be clocked by a transition

on the TOCKI pin.

On power-up, the TOCKI pin is (by default)

enabled for Timer0 in the OPTION register.

If the T0CKI pin is:

High and Timer0 is configured to transition on a

falling edge (TOSE set), or

Low and Timer0 is configured to transition on a

rising edge (TOSE clear)

Then, if the prescaler is reassigned to the WDT, a

clock pulse to the prescaler will be generated on

the reassignment.

If the prescaler is configured for the 1:1 option, the

clock pulse will incorrectly cause a WDT Time-out

Reset of the device.

Work around

1.

Disable the Timer0 external clock input by

clearing the TOCKI bit in the OPTION

register.

2.

Modify the TOSE bit in the OPTION register to

the opposite configuration for the logic level

on the T0CKI pin.

3.

Select a prescaler rate other than 1:1 and

issue a CLRWDT instruction before switching

to the final prescaler rate.

Affected Silicon Revisions

PIC16F882

PIC16F883/PIC16F884

PIC16F886/PIC16F887

A0

X

A0

X

A2

X

A0

X

A0

X

A2

X

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16CR77-I/P

IC PIC MCU 8KX14 40DIP

PIC18F45K20-I/MV

MCU 32KB FLASH 1536B RAM 40-UQFN

PIC16CR76T-I/SS

IC PIC MCU 8KX14 28SSOP

PIC18F13K50-I/P

IC PIC MCU FLASH 4KX16 20-PDIP

PIC16CR76T-I/SO

IC PIC MCU 8KX14 28SOIC

PIC18LF24K22-I/MV

IC PIC MCU 16KB FLASH 28UQFN

PIC18LF24K22-I/ML

IC PIC MCU 16KB FLASH 28QFN

PIC16CR76T-I/ML

IC PIC MCU 8KX14 28QFN

相关代理商/技术参数

PIC16F884-I/P

功能描述:8位微控制器 -MCU 7KB Flash 256 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F884-I/PT

功能描述:8位微控制器 -MCU 7KB Flash 256 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F884T-I/ML

功能描述:8位微控制器 -MCU 7KB Flash 256 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F884T-I/PT

功能描述:8位微控制器 -MCU 7KB Flash 256 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F886-E/ML

功能描述:8位微控制器 -MCU 14KB Flash 368 RAM 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F886-E/SO

功能描述:8位微控制器 -MCU 14KB Flash 368 RAM 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F886-E/SP

功能描述:8位微控制器 -MCU 14KB Flash 368 RAM 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F886-E/SP

制造商:Microchip Technology Inc 功能描述:8-Bit Microcontroller IC